CMOS(英語表記:Complementary Metal Oxide Semiconductor:相補型金属酸化膜半導体)とは半導体デバイスの名前ではなく、あくまでもp型MOSとn型MOSを組み合わせたロジック回路のことを指します。

1.CMOSの概略

CMOSとは、半導体素子の構造の一つで、金属酸化物でできた一対のp型トランジスタとn型トランジスタを組み合わせたものです。消費電力が少なく高速に動作するため、半導体製品の多くに採用されています。

また、そのような素子を組み合わせて製造された半導体チップや半導体製品のいくつかをCMOSと呼ぶ事があります。CMOSイメージセンサーやパソコンの設定などを記憶させておく不揮発性メモリの事をCMOSと呼ぶ事があります。

CMOSデバイスの重要な特性は、高い耐ノイズ性と低い静的電力消費である。 MOSFETのペアのうち1つのトランジスタは常にオフであるため、直列の組み合わせはオンとオフを切り替える際に瞬間的に大きな電力を消費するだけである。そのため、NMOSロジックやTTLのように、状態変化していないときにも定常電流が流れる論理回路ほど発熱せず、チップ上に高密度に集積することが出来ます。CMOSがVLSIチップの実装技術として最も広く使われるようになったのは、主にこのような理由によるものです。

(*)相補型:(相補型金属酸化膜半導体 (CMOS))

正電荷を持つp型トランジスタと負電荷を持つn型トランジスタの両方を使用する半導体テクノロジーです。

2.CMOSの原理

CMOS回路は、p型とn型の金属―酸化膜―半導体電界効果トランジスタ(MOSFET)を相補的に組み合わせて、論理ゲートやその他のデジタル回路を実装するものです。

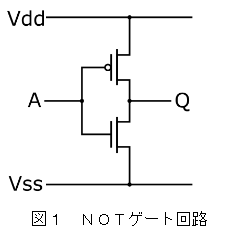

最も基本的な論理ゲートのNOTゲート(論理反転)を図1に示します。この回路において、VddとVssは電源線(VddはVssに対して3〜15V程度の電位差を持つ)で、Aが入力信号線である。Vdd側(図中上側)がPMOS-FETでありVSS側(図中下側)がNMOS-FETです。

1.AがVssと同じ電位を持つとき、上のFETがオンになり、下のFETがオフになります。このため、出力Qの電位はVddとほぼ等しくなります。

2.AがVddと同じ電位を持つとき、上のFETがオフになり、下のFETがオンになります。このため、出力Qの電位はVssとほぼ等しくなります。つまり、Aと反対の電位がQに現れる事になります。

3.CMOSの使用例(標準ロジックIC)

一般的には標準ロジックICとして論理回路で使用されています。

ここでは、標準ロジックICについて説明していきます。

標準ロジックにはTTL(英語表記:Transistor-transistor logic)・BiCMOSと今までお話しいたしましたCMOSがあります。

・TTL:

TTLはバイポーラ型ICで、標準ロジックICが普及する初期の製品です。TTLの特徴はCMOSロジックICと比べて大電流ドライブが可能なこと、動作速度が速いことですが、消費電力が大きくなります。TTLのローレベル入力電圧VIL(Max)は0.8V、ハイレベル入力電圧VIH(Min)は2.0Vになります。通称でこのレベルをTTLレベルと呼んでいます。

・CMOS:

CMOSロジックはTTLよりも低消費電力化を実現しています。初期の頃のCMOSロジックの動作はTTLよりも遅かった様ですが、現在は微細プロセスを採用する事でTTLよりも高速化を実現しています。一般的なCMOSロジック(Vcc=5V)のローレベル入力電圧VIL(Max)は1.5V、ハイレベル入力電圧VIH(Min)は3.5Vになります。なお、一部のCMOSロジックには、入力レベルをTTLレベルと互換性を持たせた製品があります。

・BiCMOS:

BiCMOSロジックは入力段と論理回路部CMOSプロセスを使用し消費電力を抑え、出力段にバイポーラトランジスターを使用して大電流ドライブを可能にしたロジックICです。MOSとバイポーラ両方のプロセスが必要なため製造プロセスが増えるためにコスト高になる様です。

3-1 インバータ

先ほどの2項での説明はインバータになります。

インバータは入力(A)の信号に対して出力(Q)が反転します。

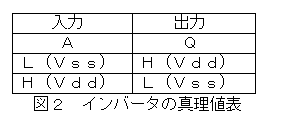

これをロジックIC表記で記載(真理値表と言います)しますと下図の様になります。

通常は入力に対して出力の状態を表しますので、単に「L」「H」のみの表記で記載します。

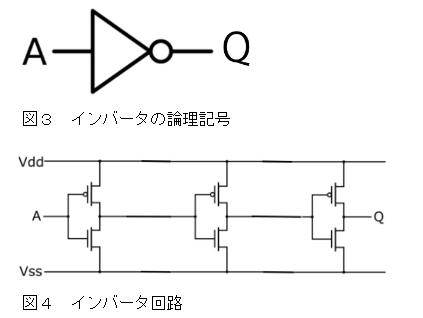

一般的なインバータは、入力の信号論理を反転させるときに用います。インバータ回路(図3)を3段使用していますので波形整形されて出力されます。

一方で、アンバッファと呼ばれるインバータがありこれはインバータ回路を1段(図1)で構成されており(波形整形はされません)、発振回路などに使用されています。

インバータを使用する際このアンバッファが必要な回路に図3の一般的なインバータ(アンバッファでないインバータ)を使用すると正常に動作しない事がありますので、注意が必要です。

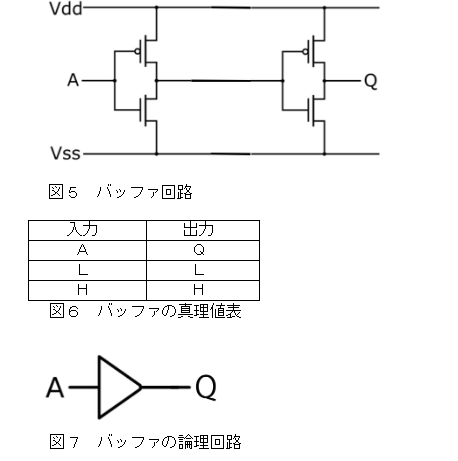

3-2 バッファ(論理変換を行いません)

バッファは入力(A)の信号に対して同相の信号(Q)が出力されます。

通常バッファは、負荷が大きい場合に駆動能力を上げる為に使用します。また長配線による寄生リアクタンスや寄生容量による信号減衰が起きる場合に波形整形を行う為に使用されます。

バッファの種類には、一つの入手力端子でデータの送信及び受信の両方ができるタイプのトランシーバ(双方向バスバッファ)と呼ばれるものがあります。トランシーバは信号を通す方向を制御信号(DIR)で切り替える事により、双方向にデータが通信するバスラインなどで使用します。

バッファ回路・真理値表・論理回路は下図の様になります。

3-3 そのほかの標準IC

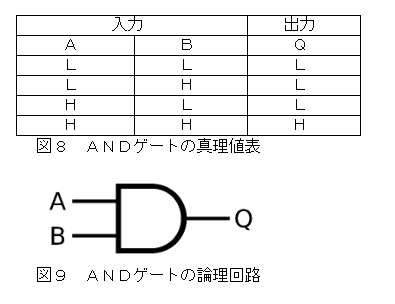

- ANDゲート

論理積の論理ゲートです。出力がHighとなるのは、ANDゲートの両方の入力がHighの場合のみです。

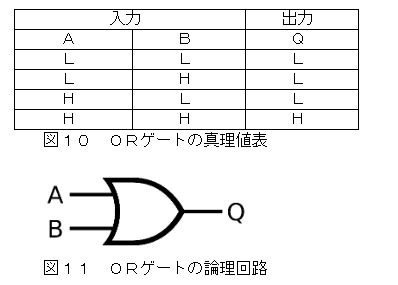

- ORゲート

論理和の論理ゲートです。入力の一方または両方がHighのとき、Highを出力し、入力がどちらもLowならLowを出力する。

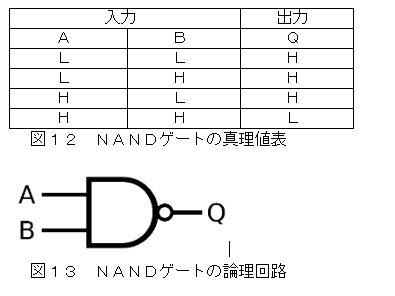

- NANDゲート

否定論理積の論理ゲートです、その(論理的な)動作は全ての入力の論理積(AND)の反転(NOT)です。全ての入力がHighの場合のみ出力がLowになり、Lowの入力がひとつでもある場合はHighを出力します。

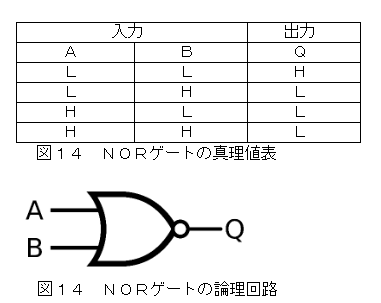

- NORゲート

否定論理和の論理ゲートです、その(論理的な)動作は、否定論理和すなわち、全ての入力の論理和(OR)をとったものの反転(NOT)です。全ての入力がLowの場合のみ出力がHighになり、Highの入力がひとつでもある場合はLowを出力します。

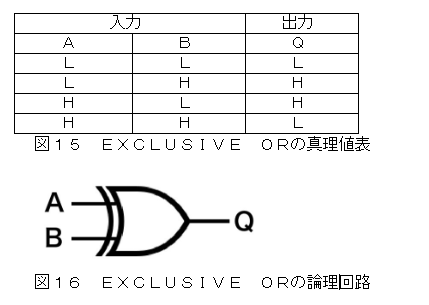

- EXCLUSIVE OR

排他的論理和の論理ゲートです、2つの入力のどちらか片方がHighでもう片方がLowの時には結果がHighとなり、両方とも真あるいは両方とも偽の時はLowとなる演算(論理演算)です。

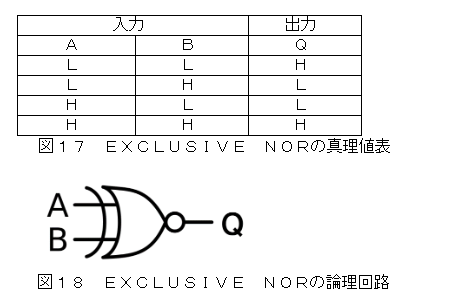

- EXCLUSIVE NOR

排他的論理和(XOR)ゲートの論理補数である機能を持つデジタル論理ゲートです。